ARM Architecture

이 문서는 영국의 Advanced RISC Machine(이하 ARM)사가 개발한 범용 32 bit RISC processor design인 ARM architecture를 개략적으로 설명합니다.

| Version | Start | Finish | Status | Contributor | Description |

|---|---|---|---|---|---|

01.00.00 | 2007.07.19 | 2007.07.30 | Done | Sungho Park | Creation and Redact |

01.00.01 | 2007.09.12 | 2007.09.12 | Done | Sungho Park | Refactoring |

01.00.02 | 2019.03.30 | 2019.03.30 | Done | Sungho Park | Move to Confluence |

목차

ARM Architecture란?

ARM architecture란 영국의 Advanced RISC Machine(이하 ARM)사가 개발한 범용 32 bit RISC processor design을 의미합니다. ARM사는 직접 processor 반도체를 제조해 판매하지 않습니다. 대신 설계한 processor를 Intellectual property(이하 IP) 형태로 제공하며, 이에 대한 license를 판매합니다. ARM processor IP는 일종의 설계도로, 여러 반도체 회사들이 여기에 필요한 주변장치들을 추가해 System On Chip(이하 SoC) 형태로 반도체를 제조해 판매합니다.

ARM architecture의 가장 큰 특징은 성능에 비해 전력 소비량이 작다는 것입니다. 때문에 휴대전화기나 PDA같은 비교적 큰 computing power가 필요하지만 전력 소비량이 작어야하는 하는 휴대용 기기 또는 내장형 기기 분야에서 많이 사용되고 있습니다.

용어 정리

ARM 관련 자료에는 ARM architecture, ARM core, ARM processor라는 용어들이 자주 나오는데, 각각의 의미는 다음과 같습니다. 먼저, ARM architecture는 명령어, 레지스터 구조, 메모리 구조 등의 processor 기본 구조와 동작원리에 대한 정의를 의미합니다. 그리고 이 ARM architecture에 따라 구현한 processor의 핵십 부분을 ARM core라고 합니다. 이 ARM core에 Cache, Memory Management Unit(이하 MMU), Memory Protection Unit(이하 MPU), Tightly Coupled Memory (이하 TCM), Bus Interface Unit (이하 BIU) 등의 핵심 주변장치들을 추가해놓은 것을 ARM processor라고 합니다. 아래 표는 ARM architecture와 그 architecture를 따르는 주요 ARM core 및 그 특징을 보여줍니다.

| Architecture | Features | Core |

|---|---|---|

| ARMv1 |

| ARM1 |

| ARMv2 |

| ARM2 |

| ARMv2a |

| ARM3 |

| ARMv3 |

| ARM6, ARM7DI |

| ARMv3M |

| ARM7M |

| ARMv4 |

| StrongARM |

| ARMv4T |

| ARM7TDMI, ARM9TDMI |

| ARMv5TE |

| ARM9E, ARM10E |

| ARMv5TEJ |

| ARM7EJ, ARM926EJ |

| ARMv6 |

| ARM11 |

Table 1. ARM Architecture 별 특징과 구현 ARM Core 예

ARM core는 특징에 따라 몇 개의 family로 구분합니다. 아래 표는 ARM core family와 그 familiy에 속하는 ARM core의 대략적인 특징을 보여줍니다.

| ARM7 | ARM9 | ARM10 | ARM11 | |

|---|---|---|---|---|

| 파이프라인 단계 | 3 | 5 | 6 | 8 |

동작 주파수 (MHz) | 125 | 220 ~ 250 | 266 ~ 325 | 400 |

| 전력 소비량 (mW/MHz) | 0.06 | 0.4 (+cache) | 0.5 (+cache) | 0.4 (+cache) |

| 성늘 (MIPS/MHz) | 0.9 | 1.1 | 1.3 | 1.2 |

| 구조 | Von Neumann | Harvard | Harvard | Harvard |

| ||||

Table 2. ARM Core Family 별 특징

ARM architecture, ARM core, 또는 ARM processor 이름에 포함된 알파벳과 숫자의 의미는 다음과 같습니다.

ARM [a] [b] [T] [D] [M] [I] [E] [J] [F] [-S] a : 속한 ARM core family b : memory management unit, memory protection unit, cache, TCM 구성 T : Thumb 명령 지원 D : 디버그 기능 지원 M : 64 bit 결과를 내는 곱셈기 지원 I : In-Circuit Emulator(이하 ICE) 기능 지원 E : DSP 성능 향상을 위한 명령(Enhanced DSP 명령) 지원 J : Java bytecode 성능 향상을 위한 명령(Jazelle 기술) 지원 F : Vector Floating-Point(이하 VFP) 구조 지원 -S: Electronic Design Automation(이하 EDA) 도구로 synthesis 할 수 있음

예를 들어, ARM926EJ-S의 “9”는 ARM 9 family에 속함을, “26”은 MMU와 cache 그리고 TCM 지원을, “E”는 DSP 성능 향상을 위한 명령(Enhanced DSP 명령) 지원을, J는 Java bytecode 성능 향상을 위한 명령(Jazelle 기술) 지원을, -S는 EDA 도구로 synthesis 할 수 있음을 의미합니다. 그리고 ARM 9 family 부터는 대부분 “T”, “D”, “M”, “I” 가 나타내는 기능들을 기본적으로 포함하기 때문에 이 알파벳들은 생략합니다.

Programmer's Model

Programmer's model이란 프로그래머가 프로그램을 작성하기 위해 필요한 정보를 의미합니다. 명령어, 메모리 구조, 동작 모드, 레지스터, 예외처리 방법, 인터럽트 처리 방법 등이 이에 해당합니다. 이 programmer’s model은 ARM architecture에 따라 조금씩 달라집니다.

ARMv4T Architecture의 Programmer's Model

Instuction Set (명령어)

32-bit ARM instruction set과 16-bit Thumb instruction set을 지원합니다. ARM instruction set은 ARM state에서, Thumb instruction set은 Thumb state에서 각각 실행되며, ARM / Thumb state 간의 전환은 BX instruction을 사용해 이루어집니다.

Memory Format (메모리 구조)

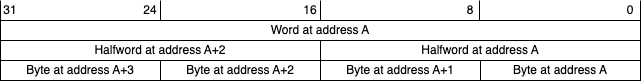

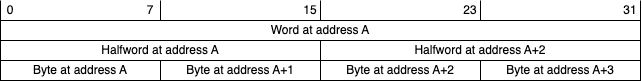

기본 설정은 little-endian이지만, big-endian도 지원합니다. 아래 그림은 Little-endian일 경우와 Big-endian일 경우의 halfword와 byte 순서를 보여줍니다. (ARM 관련 문서에서 word는 4 byte 입니다.)

Figure 1. Halfword and Byte Order of Little-endian

Figure 2. Halfword and Byte Order of Big-endian

Operating Mode (동작 모드)

다음과 같은 7개의 operating mode가 존재합니다.

- User mode

- 일반적인 프로그램들이 동작하는 모드로, 대부분의 응용프로그램들이 이 모드에서 동작합니다. 이 모드는 다른 6개의 모드와 달리 유일하게 privileged mode 가 아닙니다. 때문에 일부 중요 시스템 자원 접근이 제한됩니다.

- Fast Interrupt mode (이하 FIQ mode)

- Fast interrupt를 처리하는 모드.

- Interrupt mode (이하 IRQ mode)

- 일만 interrupt를 처리하는 모드.

- Supervisor mode

- Reset 후 또는 software interrupt (이하 SWI)가 발생했을 때 이 모드로 전환됩니다. 주로 운영체제가 이 모드를 사용합니다.

- Abort mode

- Data 또는 instruction prefetch에 실패했을 때 이 모드가 됩니다.

- System mode

- User mode 와 같이, 외부 요청이 아닌 소프트웨어의 요청(Current Program Status Register를 직접 수정)에 의해 전환되는 모드로, 주로 운영체제가 이 모드를 사용합니다.

- Undefined mode

- 정의되지 않은 instruction을 실행하려고 했을 때 이 모드로 전환됩니다.

Register

총 37개의 register가 있으며, 이들 중 31개는 general purpose register이고, 6개는 status register 입니다.

ARM State Registers

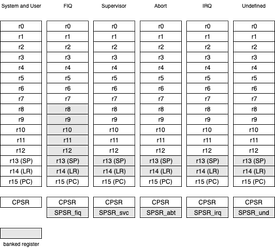

ARM state일 경우, 16개의 general purpose register와 1개 또는 2개의 status register를 사용할 수 있습니다. 아래 그림은 ARM state일 경우의 register 구성을 보여줍니다.

Figure 3. ARM State Registers

위 그림에서 진하게 표시된 것은 banked register로, 같은 이름으로 접근하지만 해당 operating mode 일때 다른 operating mode 일 때와는 다른 독립적인 값을 가집니다 Register r13은 일반적으로 stack point(이하 SP)로 사용하며, register r14는 함수 호출(BL 또는 BLX instruction 사용) 시 복귀할 주소를 저장하는 link register(이하 LR)로 사용합니다. 그리고 register r15는 다음에 수행할 instruction 주소를 저장하는 program counter(이하 PC)로 사용합니다. FIQ mode일 경우는 특별히 register r8~r12 역시 banked register입니다. 때문에 FIQ mode에서 수행되는 FIQ handler는 진입할 때 이전 register 값을 저장했다가 복귀할 때 register를 이전 값으로 되돌리는 작업을 해 줄 필요가 없습니다. 때문에 FIQ handler는 원하는 작업을 IRQ handler에 비해 빠르게 처리할 수 있습니다. Current Porgram Status Register (이하 CPSR)는 이름 그대로 현재 상태 정보를 저장하고 있습니다. 이 register가 담고 있는 내용은 이후에 따로 자세히 설명하겠습니다. Saved Program Status Register (이하 SPSR)는 현재 operating mode로 들어가지 직전 operating mode의 상태 정보를 담고 있습니다. 내용은 CPSR과 동일합니다.

Thumb State Registers

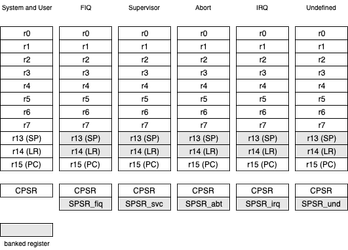

아래 그림은 Thumb state일 때 접근 가능한 register들을 보여줍니다. 일부를 제외한 대부분의 instruction들의 경우, ARM state일 때와는 달리 아래 그림에 표시되지 않은 r8~r12를 사용할 수 없습니다. 이 차이점을 제외하면 다른 내용은 ARM state일 경우와 동일합니다.

Figure 4. Thumb State Registers

Program Status Register (CPSR, SPSR)

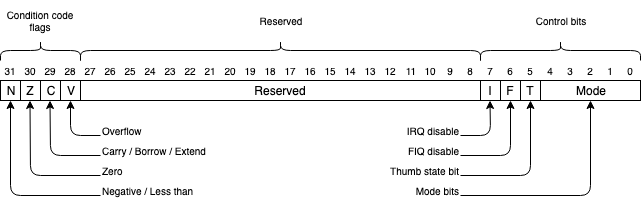

Program status register는 가장 최근에 수행된 ALU operation의 결과에 대한 정보(condition code flags)를 저장하고 있습니다. 그리고 interrupt disable 여부, operating mode, operating state에 대한 정보도 함께 가지고 있습니다. Program status register는 두 종류가 있는데, 그중 하나인 CPSR은 현재 상태 정보를 담고 있으며, 다른 하나인 SPSR은 현재 operating mode로 변경되기 직전의 상태 정보를 담고 있습니다.. 아래 그림은 program status register의 bit 구조를 보여줍니다.

Figure 5. ARMv4T Architecture Program Status Register Bits

각 bit의 의미는 다음과 같습니다.

- N

- 연산 결과가 음수이면 1, 그렇지 않으면 0

- Z

- 연산 결과가 0이면 1, 그렇지 않으면 0

- C

- 비교 기능을 포함한 덧셈 연산에서 carry (unsigned overflow)가 발생하면 1, 그렇지 않으면 0

- 비교 기능을 포함한 뺄셈 연산에서 borrow (unsigned underflow)가 발생하면 0, 그렇지 않으면 1

- Shift 연산에서 범위 밖으로 벗어난 마지막 bit가 1이면 1, 그렇지 않으면 0

- V

- 덧셈 또는 뺄셈 연산에서 signed overflow가 발생하면 1, 그렇지 않으면 0

- I

- 1이면 IRQ가 disable

- F

- 1이면 FIQ가 disable

- T

- 1이면 Thumb state

M

M[4:0] Mode 10000 User 10001 Fast interrupt 10010 Interrupt 10011 Supervisor 10111 Abort 11111 System 11011 Undefined Table 3. Mode Bits

Exception

Exceptioin은 오류가 발생했거나 외부 장치의 요청(interrupt)이 들어와서 현재 수행중인 프로그램을 잠시 멈추고 발생한 오류 또는 요청(interrupt)을 먼저 처리하는 상황을 의미합니다. 이 exception handling은 ARM state에서만 가능하기 때문에, exception handler는 ARM instruction set으로 작성해야 합니다. Exception이 발생하면 다음과 같은 과정을 거쳐 exception을 처리하는 exception vector가 실행됩니다.

- PC를 LR에 복사

- CPSR을 SPSR에 복사

- Operating mode 변경

- Operating state를 ARM state로 변경

- 필요에 따라 interrupt을 disable 시킴

- PC를 해당 exception vector 주소로 변경

Exception 처리가 끝나면 다음과 같은 과정을 거쳐 다시 exception이 발생하기 직전에 수행 중이던 프로그램으로 복귀합니다.

- LR에 저장된 값을 참조해 PC 값 복원

- SPSR에 저장된 값으로 CPSR 복원

Exception은 아래와 같은 6종류가 있습니다.

- Reset

- nRESET signal에 low 신호가 들어오면 발생합니다. 시스템을 reset 시키기 위해 사용합니다.

- FIQ

- nFIQ signal에 low 신호가 들어오면 발생합니다. FIQ를 처리하기 위해 사용합니다.

- IRQ

- nIRQ signal에 low 신호가 들어오면 발생합니다. IRQ를 처리하기 위해 사용합니다.

- Abort

- 메모리 접근에 실패했을 때 발생합니다. Abort exception은 아래와 같은 두가지 종류가 있습니다.

- Prefetch Abort (이하 PABT)

- 메모리에서 실행할 instruction을 가져오는(prefetch) 단계에서 문제가 생기면 이 exception이 발생합니다. Exception이 발생하는 시점은 메모리에 접근을 시도한 시점이 아니라 문제의 instruction이 pipeline의 execute stage에 도달했을 때입니다.

- Data Abort (이하 DABT)

- 메모리에서 데이터를 가져올 때 문제가 생기면 이 exception이 발생합니다. 이 exception은 메모리에 접근을 시도한 시점에서 발생합니다.

- SWI

- SWI instruction을 사용해 소프트웨어가 직접 발생시킵니다. 주로 supervisor mode 권한을 얻기 위해 사용합니다. 운영체제가 주로 사용합니다.

- Undefined instruction

- 정의되지 않은 instruction을 실행하려 할 때 발생합니다.

아래 표는 exception 처리를 끝낸 후 원래의 code로 복귀하는 명령과 exception이 발생했을 때 r14에 저장되는 값을 보여줍니다.

| Entry | Return Instruction | r14(LR) (ARM State) | r14(LR) (Thumb State) |

|---|---|---|---|

| SWI | MOVS PC, R14_svc | PC+4 | PC+2 |

| UDEF | MOVS PC, R14_und | PC+4 | PC+2 |

| PABT | SUBS PC, R14_abt, #4 | PC+4 | PC+4 |

| FIQ | SUBS PC, R14_fiq, #4 | PC+4 | PC+4 |

| IRQ | SUBS PC, R14_irq, #4 | PC+4 | PC+4 |

| IDABT | SUBS PC, R14_abt, #8 | PC+8 | PC+8 |

| RESET | Not applicable |

Table 4. Exception Return Instruction

두개 이상의 Exception이 동시에 발생하면 아래 표에 명시된 우선순위에 따라 처리됩니다.

| Priority | Exception |

|---|---|

| Highest | Reset |

| Data Abort | |

| FIQ | |

| IRQ | |

| Prefetch Abort | |

| Lowest | Undefined Instruction, SWI |

Table 5. Exception Priority Order

아래 표는 각 exception 별로 exception을 처리하는 exception vector의 주소, exception을 처리할 때의 operating mode, 그리고 IRQ와 FIQ disable 여부를 보여줍니다.

| Address | Exception | Mode on Entry | IRQ (I State on Entry) | FIQ (F State on Entry) |

|---|---|---|---|---|

| 0x00000000 | Reset | Supervisor | Disabled | Disabled |

| 0x00000004 | Undefined Instruction | Undefined | Disabled | Unchanged |

| 0x00000008 | Software Instruction | Supervisor | Disabled | Unchanged |

| 0x0000000C | Prefetch Abort | Abort | Disabled | Unchanged |

| 0x00000010 | Data Abort | Abort | Disabled | Unchanged |

| 0x00000014 | Reserved | |||

| 0x00000018 | IRQ | IRQ | Disabled | Unchanged |

| 0x0000001C | FIQ | FIQ | Disabled | Disabled |

Table 6. Exception Vectors

ARMv5TEJ Architecture의 Programmer's Model

Instruction Set (명령어)

ARMv4T Architecture의 확장판으로 향상된 ARM과 Thumb state 간 전환 명령, DSP 성능 향상을 위한 명령, Java bytecode 수행 성능 향상을 위한 명령이 추가되었습니다.

Memory Format (메모리 구조)

ARMv4T Architecture와 동일합니다.

Operating Mode (동작 모드)

ARMv4T Architecture와 동일합니다.

Register

ARMv4T Architecture와 동일합니다.

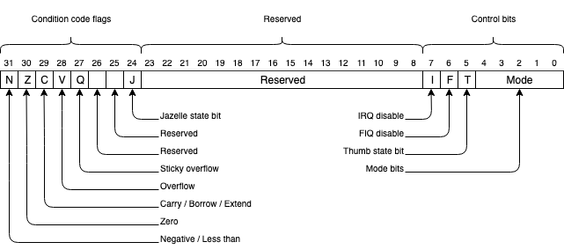

Program Status Register (CPSR, SPSR)

Program status register의 bit 구조는 아래 그림과 같습니다.

Figure 5. ARMv5TEJ Architecture Program Status Register Bits

Q, J bit가 추가된 것 외에는 ARMv4T Architecture와 동일합니다. Q는 enhanced DSP instruction을 수행했을 때 overflow 또는 saturation이 발생하면 1, 그렇지 않으면 0값을 가집니다. J는 현재 상태가 Jazelle state일 경우 1, 그렇지 않을 경우 0 값을 가집니다.

Exception

Breakpoint instruction exception이 추가되었습니다. 이 exception은 BKPT instruction을 처리하는 하드웨어가 추가되어 있지 않은 환경에서 이 instruction을 수행할 때 발생하며, prefetch abort exception vector에서 처리합니다. 우선 순위는 가장 낮습니다. Control bit functions register c1의 location of exception vectors 값을 수정해 exception vector location을 변경할 수 있게 되었습니다. 이 값이 0이면 exception vector base address가 0x00000000이 되며, 1이면 0xFFFF0000이 됩니다. 이 두가지 사항 외에는 ARMv4T Architecture와 동일합니다.

참고 자료

- ARM v5TE Architecture Reference Manual

- ARM7TDMI r4p1 Technical Reference Manual

- ARM9EJ-S Revision r1p2 Technical Reference Manual

- ARM926EJ-S r0p4 r0p5 Technical Reference Manual

- http://www.arm.com

- ARM System Developer’s Guide - Designing and Optimizing System Software

- ARM으로 배우는 임베디드 시스템